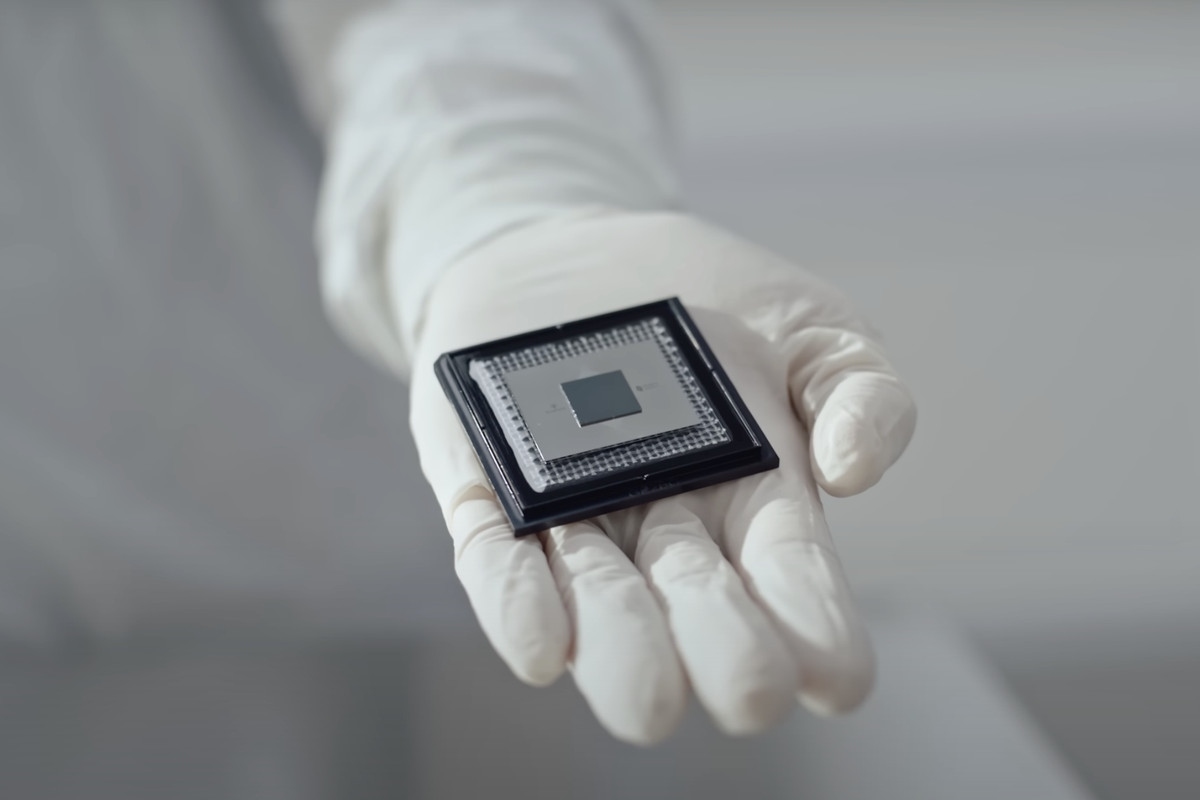

Gli scienziati cinesi hanno sviluppato un chip in grado di eseguire calcoli 1.000 volte più velocemente rispetto al chip più avanzato dell’attuale leader del mercato dell’intelligenza artificiale, Nvidia, con un consumo energetico molto inferiore. Si tratta di un risultato straordinario di per sé, ma la cosa davvero sorprendente è che non si tratta di un chip digitale (che comunica in binario), bensì di un chip analogico, cosa che fino ad ora era ritenuta impossibile. Secondo i risultati del loro studio, revisionato da esperti del settore e pubblicato sulla prestigiosa rivista scientifica occidentale Nature electronics, la loro invenzione ha la precisione e la scalabilità necessarie per rivoluzionare la tecnologia moderna.

Calcoli in memoria: un chip rivoluzionario

La differenza tra calcolo analogico e digitale è fondamentale per comprendere la portata di questo progresso. Un computer digitale funziona come un interruttore della luce: comprende solo due stati, acceso (1) o spento (0). Tutte le informazioni si riducono a questa semplice dualità. Un computer analogico, invece, è come un regolatore di intensità: utilizza uno spettro continuo di valori per rappresentare le informazioni. Questa idea non è nuova. Il meccanismo di Antikythera, un calcolatore astronomico dell’antica Grecia, è l’esempio più antico che si conosca. Tuttavia, l’informatica analogica è stata relegata alla categoria delle tecnologie obsolete a causa di un problema insormontabile: la mancanza di precisione.

Il team dell’Università di Pechino ha risolto quello che il suo autore, il professor Sun Zhong, descrive come un “problema che ha sconcertato la comunità scientifica mondiale per un secolo”. Il loro progresso si basa su un approccio ibrido che utilizza memorie ad accesso casuale resistive (RRAM, un tipo di memoria che memorizza i dati alterando la resistenza elettrica di un materiale) e un algoritmo iterativo per risolvere equazioni matriciali complesse. Eseguendo i calcoli direttamente nella memoria, il chip evita il collo di bottiglia dell’architettura informatica tradizionale, in cui i dati devono viaggiare costantemente tra il processore e la memoria, un processo lento che consuma un’enorme quantità di energia.

Cos’è e come funziona

Il cuore di questa nuova macchina è un chip di memoria resistiva. A differenza della memoria digitale, che memorizza zeri e uno, una cella di memoria RRAM funziona modificando la sua resistenza elettrica a un livello specifico. Immaginate di poter regolare la resistenza di un materiale come se fosse la corda di una chitarra in modo che rappresenti un valore numerico esatto. I ricercatori sono riusciti a programmare in modo affidabile otto livelli diversi di conduttanza – la facilità con cui un materiale lascia passare la corrente elettrica, cioè il contrario della resistenza – in ogni cella, il che equivale a una risoluzione di 3 bit.

Il vero potere di questo chip si sprigiona quando risolve equazioni matriciali, un insieme di operazioni matematiche fondamentali per l’IA, la base matematica dell’intelligenza artificiale, della simulazione scientifica e dell’elaborazione dei segnali. Un computer digitale affronta questi problemi in modo sequenziale, eseguendo miliardi di operazioni passo dopo passo. Il chip analogico, invece, converte la matrice di numeri in una matrice fisica di resistenze elettriche. Applicando tensioni, il circuito risolve l’equazione quasi istantaneamente grazie alle leggi della fisica, eseguendo una moltiplicazione matrice-vettore in un unico passaggio.

La chiave per superare il problema storico della precisione analogica è un ingegnoso algoritmo iterativo. Il processo combina due operazioni puramente analogiche: un’inversione di matrice a bassa precisione e una moltiplicazione matrice-vettore ad alta precisione. Il sistema esegue prima un calcolo rapido ma approssimativo per ottenere una soluzione iniziale. Successivamente, utilizza l’operazione ad alta precisione per affinare il risultato in cicli successivi, correggendo l’errore fino a raggiungere l’accuratezza desiderata. Come affermano gli autori nel loro studio, “[l]a precisione è stata a lungo il principale collo di bottiglia del calcolo analogico”. Questo metodo lo supera.

Per ottenere un’elevata precisione paragonabile a quella dei sistemi digitali, il chip utilizza una tecnica nota come “bit-slicing”: un numero ad alta precisione (ad esempio, a 24 bit) viene scomposto in diversi frammenti a bassa precisione (a 3 bit), che le celle RRAM sono in grado di gestire. I risultati parziali vengono ricombinati per ottenere la soluzione finale ad alta precisione. Per la scalabilità, ovvero la capacità del sistema di gestire in modo efficiente problemi sempre più grandi, gli scienziati hanno applicato un algoritmo chiamato BlockAMC, che divide una matrice gigante in blocchi più piccoli che il chip può elaborare in modo distribuito. Nei loro esperimenti, hanno risolto una matrice 16×16 con una precisione di 24 bit, un livello paragonabile a quello dei processori digitali a 32 bit (FP32).

Un caso d’uso reale

Per dimostrare la capacità della loro invenzione, il team l’ha applicata al rilevamento dei segnali in un sistema di comunicazione Massive MIMO, una tecnologia wireless che utilizza un gran numero di antenne per migliorare la velocità e la qualità della connessione, fondamentale per le reti 5G e 6G. Questo compito richiede un’immensa capacità di calcolo per elaborare in tempo reale i segnali che viaggiano tra le molteplici antenne di una stazione base e i dispositivi degli utenti. Il chip analogico è stato in grado di svolgere questo compito in un sistema di 128 antenne con modulazione ad alta densità (il processo di conversione dei dati digitali in segnali analogici per la trasmissione) di tipo 256-QAM, raggiungendo le stesse prestazioni di un processore digitale FP32 in soli tre cicli di iterazione. Dopo due cicli, l’immagine trasmessa per il test è stata ricostruita con assoluta fedeltà.

Le implicazioni di questo progresso sono profonde. Secondo le stime del team, il loro approccio potrebbe offrire “prestazioni 1.000 volte superiori e un’efficienza energetica 100 volte migliore rispetto ai processori digitali di ultima generazione a parità di precisione”. Sebbene esistano ancora delle sfide per la produzione di circuiti di inversione su larga scala in un unico chip, i ricercatori concludono che il loro sistema dimostra una strada percorribile. Il futuro pratico prevede l’integrazione di questi moduli in chip dedicati per accelerare compiti specifici in data center, supercomputer e dispositivi di intelligenza artificiale, aprendo una nuova era per l’informatica.